Deck 5: Combinational Logic Analysis

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

سؤال

فتح الحزمة

قم بالتسجيل لفتح البطاقات في هذه المجموعة!

Unlock Deck

Unlock Deck

1/38

العب

ملء الشاشة (f)

Deck 5: Combinational Logic Analysis

1

The NAND gate is an example of combinational logic.

True

2

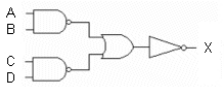

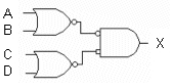

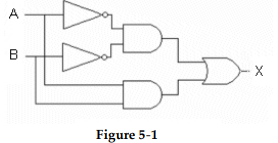

This circuit is an example of the implementation of AND- OR- INVERT logic.

False

3

The commonly accepted abbreviation for an exclusive- OR gate is XOR.

True

4

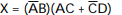

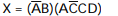

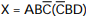

is in the form of a sum- of- products expression.

is in the form of a sum- of- products expression.

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

5

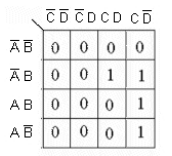

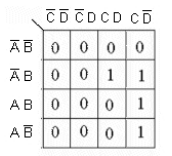

The Karnaugh map below represents the expression, X = ACD + AB(CD + BC).

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

6

NAND gates cannot be used to construct NOR gates.

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

7

NOR gates can be used to construct AND gates.

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

8

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

9

The effect of an inverted output being connected to the inverting input of another gate is to effectively eliminate one of the inversions, resulting in a single inversion.

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

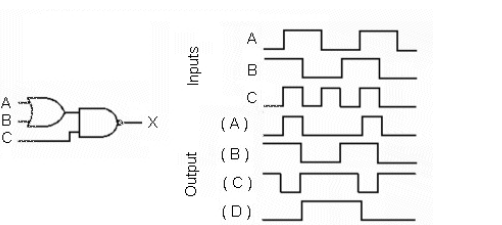

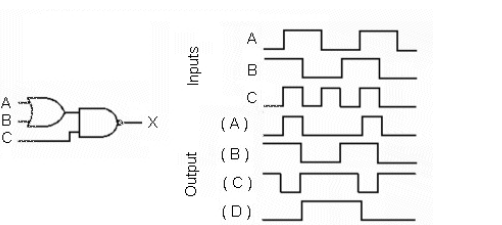

10

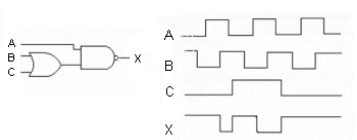

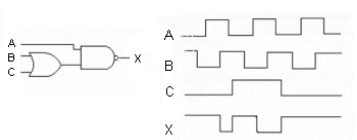

The waveforms are correct for the logic circuit shown.

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

11

The reason that NOR logic networks are often drawn as shown in this figure, is _________.

A) to make it easier to determine the logical output

B) to help make the transition to a K- map

C) that it shows the actual gate arrangement

D) to minimize the number of parts required

A) to make it easier to determine the logical output

B) to help make the transition to a K- map

C) that it shows the actual gate arrangement

D) to minimize the number of parts required

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

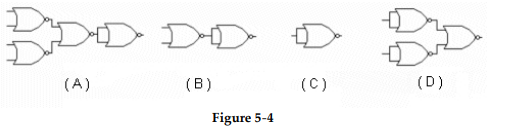

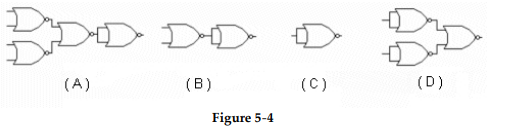

12

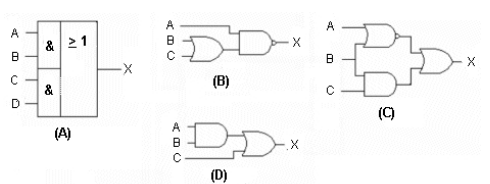

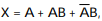

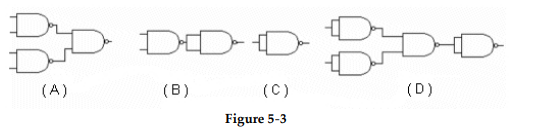

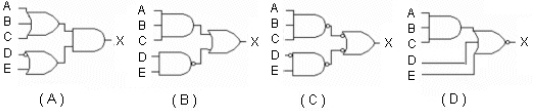

Which figure below represents AND- OR logic?

A) Figure (A)

B) Figure (B)

C) Figure (C)

D) Figure (D)

A) Figure (A)

B) Figure (B)

C) Figure (C)

D) Figure (D)

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

13

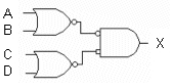

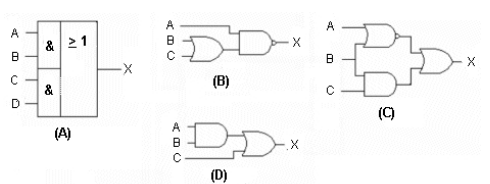

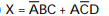

-Which of the following logic expressions represents the logic diagram in Figure 5- 1?

A) X = AB + AB

B)

C)

D)

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

14

-What type of logic circuit is represented by Figure 5- 1?

A) XOR

B) XNAND

C) XAND

D) XNOR

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

15

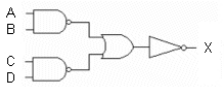

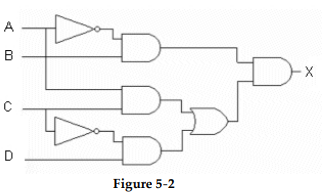

-A correct logic expression for Figure 5- 2 is _________.

A)

B)

C)

D)

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

16

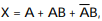

How many gates, including inverters, are required to implement the equation,  as it is written?

as it is written?

A) 1

B) 2

C) 3

D) 4

as it is written?

as it is written?A) 1

B) 2

C) 3

D) 4

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

17

How many gates, including inverters, are required to implement the equation,  after it is simplified using Boolean algebra?

after it is simplified using Boolean algebra?

A) 1

B) 2

C) 3

D) 4

after it is simplified using Boolean algebra?

after it is simplified using Boolean algebra?A) 1

B) 2

C) 3

D) 4

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

18

The NAND gate is referred to as a "universal" gate, because it_________.

A) is used in all the countries of the world

B) can be found in almost all digital circuits

C) can be used to build all the other types of gates

D) was the first gate to be integrated

A) is used in all the countries of the world

B) can be found in almost all digital circuits

C) can be used to build all the other types of gates

D) was the first gate to be integrated

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

19

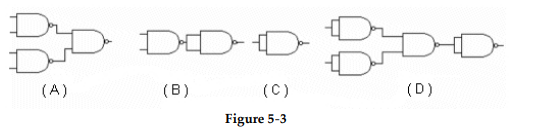

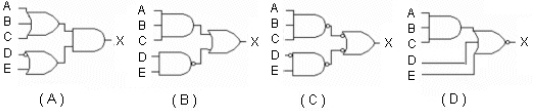

-Which circuit in Figure 5- 3 represents the NAND implementation of a NOR gate?

A) Figure (A).

B) Figure(B) .

C) Figure (C).

D) Figure (D).

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

20

-Which circuit in Figure 5- 3 represents the NAND implementation of an AND- OR function?

A) Figure (A).

B) Figure (B).

C) Figure (C).

D) Figure (D).

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

21

-Which circuit in Figure 5- 3 represents the NAND implementation of an inverter?

A) Figure (A).

B) Figure (B).

C) Figure (C).

D) Figure (D).

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

22

The relationship between a NAND gate and a negative- OR gate is expressed by__________.

A)

B)

C)

D)

A)

B)

C)

D)

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

23

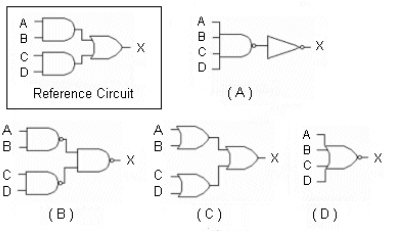

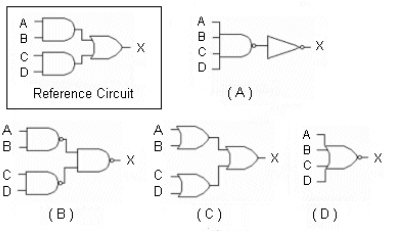

Which circuit is the logical equivalent of the Reference Circuit?

A) Figure (A)

B) Figure (B)

C) Figure (C)

D) Figure (D)

A) Figure (A)

B) Figure (B)

C) Figure (C)

D) Figure (D)

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

24

When the inverted output of one gate is connected to the inverted input of another gate, __________.

A) one inversion cancels the other and only a single inversion results

B) the inversions cancel

C) a double inversion occurs and the signal is inverted

D) all of the above are correct

A) one inversion cancels the other and only a single inversion results

B) the inversions cancel

C) a double inversion occurs and the signal is inverted

D) all of the above are correct

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

25

Why are multiple NAND gates often used in place of other single function gates?

A) It is easier to design logic circuits with a single gate type, since you only have to fully understand how one type of gate works.

B) It makes it possible to use spare portions of NAND IC packages to implement other logic functions, perhaps reducing the total IC package count.

C) NAND gates are cheaper than any other type of gate.

D) NAND gates are packaged more densely on IC's than other types of gates.

A) It is easier to design logic circuits with a single gate type, since you only have to fully understand how one type of gate works.

B) It makes it possible to use spare portions of NAND IC packages to implement other logic functions, perhaps reducing the total IC package count.

C) NAND gates are cheaper than any other type of gate.

D) NAND gates are packaged more densely on IC's than other types of gates.

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

26

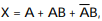

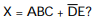

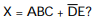

Which of the figures is the correct NAND logic implementation of the expression,

A) Figure (A)

B) Figure (B)

C) Figure (C)

D) Figure (D)

A) Figure (A)

B) Figure (B)

C) Figure (C)

D) Figure (D)

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

27

The relationship between a NOR gate and a negative- AND gate is expressed by .

A)

B)

C)

D)

A)

B)

C)

D)

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

28

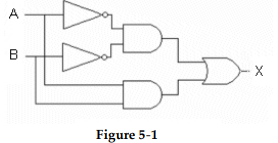

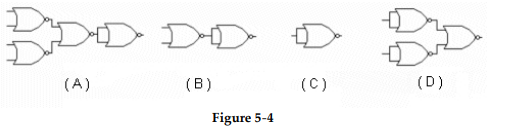

-Which circuit in Figure 5- 4 represents the NOR implementation of an OR gate?

A) Figure (A)

B) Figure (B)

C) Figure (C)

D) Figure (D)

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

29

-Which circuit in Figure 5- 4 represents the NOR implementation of an AND gate?

A) Figure (A)

B) Figure (B)

C) Figure (C)

D) Figure (D)

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

30

-Which circuit in Figure 5- 4 represents the NOR implementation of an inverter?

A) Figure (A)

B) Figure (B)

C) Figure (C)

D) Figure (D)

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

31

Which output waveform is correct for the circuit input waveforms shown?

A) Output (A)

B) Output (B)

C) Output (C)

D) Output (D)

A) Output (A)

B) Output (B)

C) Output (C)

D) Output (D)

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

32

The point identified as 'X' in this figure is referred to as _______.

A) a reference point

B) a node

C) common

D) a tie point

A) a reference point

B) a node

C) common

D) a tie point

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

33

What is the indication of an open in the output of a driving gate?

A) Only the output of the defective gate is affected.

B) The affected node will be stuck in the HIGH state.

C) There is a signal loss to all load gates.

D) The affected node will be stuck in the LOW state.

A) Only the output of the defective gate is affected.

B) The affected node will be stuck in the HIGH state.

C) There is a signal loss to all load gates.

D) The affected node will be stuck in the LOW state.

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

34

What is the indication of a short to ground in the output of a driving gate?

A) The affected node will be stuck in the HIGH state.

B) The node is stuck in the LOW state.

C) Only the output of the defective gate is affected.

D) There is a signal loss to all load gates.

A) The affected node will be stuck in the HIGH state.

B) The node is stuck in the LOW state.

C) Only the output of the defective gate is affected.

D) There is a signal loss to all load gates.

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

35

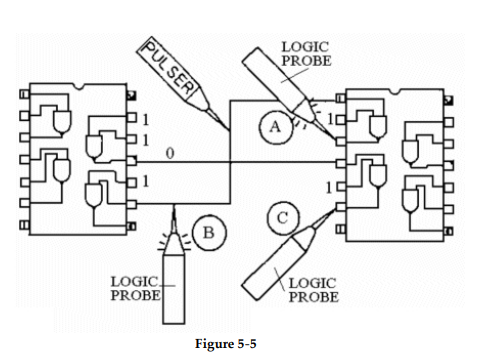

-Based on the indications of probe A in Figure 5- 5, what, if anything, is wrong with the circuit?

A) The logic probe is unable to determine the state of the circuit at that point and is blinking to alert the technician to the problem.

B) The output appears to be LOW, but is being pulsed by the pulser.

C) The output appears to be shorted to Vcc, but is being pulsed by the pulser.

D) Nothing appears to be wrong at that point.

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

36

-Based on the indications of probe C in Figure 5- 5, what, if anything, is wrong with the circuit?

A) The gate appears to be working correctly.

B) Pin 6 on the right- hand IC is shorted to ground.

C) The gate being tested has not been connected to Vcc and ground.

D) Pin 5 on the right- hand IC appears to be open.

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

37

The output of a gate has an internal short. A current tracer will ________.

A) be able to identify the defective load node

B) probably not be able to locate the problem

C) identify the defective gate

D) show whether the gate is shorted to Vcc or ground

A) be able to identify the defective load node

B) probably not be able to locate the problem

C) identify the defective gate

D) show whether the gate is shorted to Vcc or ground

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck

38

An output gate is connected to four input gates; the circuit does not function. Preliminary tests with a DMM indicate that power is applied; scope tests show that the primary input gate has a pulsing signal, while the interconnecting node has no signal. The four load gates are all on different IC's. Which instrument will best help isolate the problem?

A) Oscilloscope

B) Logic analyzer

C) Current tracer

D) Logic probe

A) Oscilloscope

B) Logic analyzer

C) Current tracer

D) Logic probe

فتح الحزمة

افتح القفل للوصول البطاقات البالغ عددها 38 في هذه المجموعة.

فتح الحزمة

k this deck